# Introduzione CUDA hardware Programmazione CUDA CUDA software architecture GPU memory management Ottimizzazione dell'accesso ai dati Sincronizzazione Aspetti di calcolo Conclusioni

#### NVIDIA CUDA world...

- \* CUDA hardware

- > Schede grafiche NVIDIA (GeForce, Quadro)

- > Sistemi NVIDIA high-performance computing (HPC) (Tesla)

- \* CUDA software

- > **CUDA** language (estensione di C)

- > Librerie per programmazione ad alto livello

- CUBLAS (algebra lineare), CUFFT (calcolo FFT): non è necessario imparare CUDA per utilizzarle!

A A 2009/1

F. Pedersini – DSI, UniM

CUDA - 3/49

#### Perchè fare calcolo con le GPU? GT200 \* Performance... > GeForce GT 280: Peak GFLOP/s > 900 MFLOPS/sG71 > Xeon 3.2 GHz: 3.2 GHz $\sim 90~\mathrm{MFLOPS/s}$ ...a costi da produzione di 2008 massa! > GeForce GT 280: - 240 processori - 1 GB RAM a bordo < 400 € GT200 = GeForce GTX 280 NV35 = GeForce FX 5950 Ultra G71 = GeForce 7900 GTX G92 = GeForce 9800 GTX G70 = GeForce 7800 GTX NV30 = GeForce FX 5800 G80 = GeForce 8800 GTX NV40 = GeForce 6800 Ultra

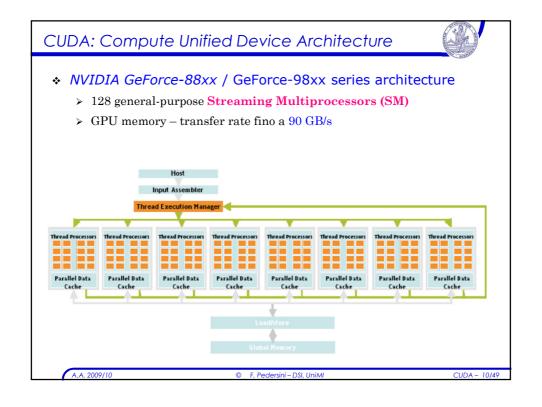

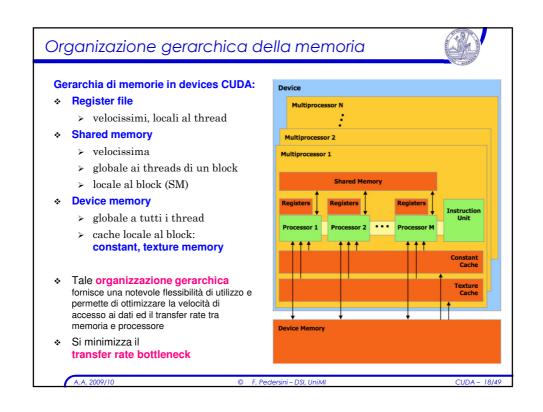

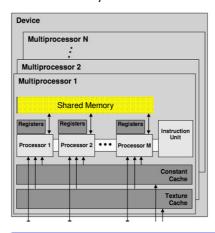

#### CUDA: architettura hardware

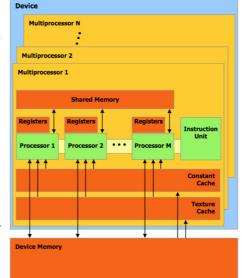

- \* Device CUDA: array di Multiprocessori

- \* Streaming Multiprocessor (SM)

- Uno SM contiene M processori, in grado di eseguire threads in parallelo in modalità SIMD: eseguono la stessa istruzione su dati diversi

- Uno SM è in grado di eseguire un warp di threads (32 threads)

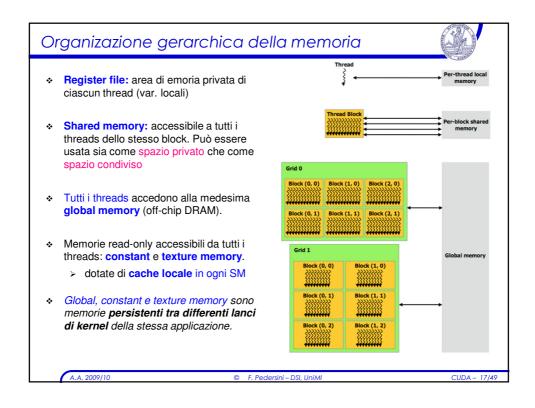

- Organizzazione gerarchica della memoria

- Register file spazio privato di ogni singolo processore

- Shared memory, condivisa da tutti i processori di uno stesso Multiprocessore

- Read-only constant cache, per lettura accelerata di costanti

- Read-only texture cache, ottimizzata per la lettura di textures

- **Device memory**, esterna ai Multiprocessori: spazio condiviso

A.A. 2009/10

F. Pedersini – DSI, UniA

CUDA - 11/49

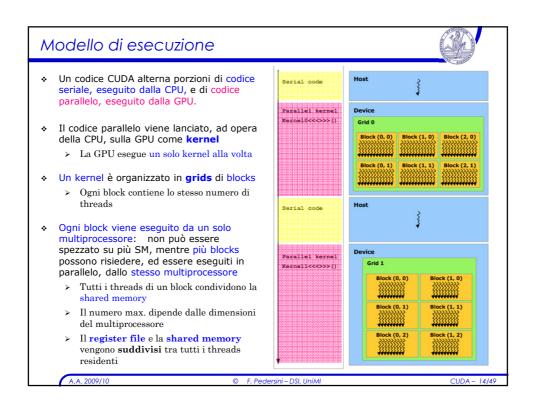

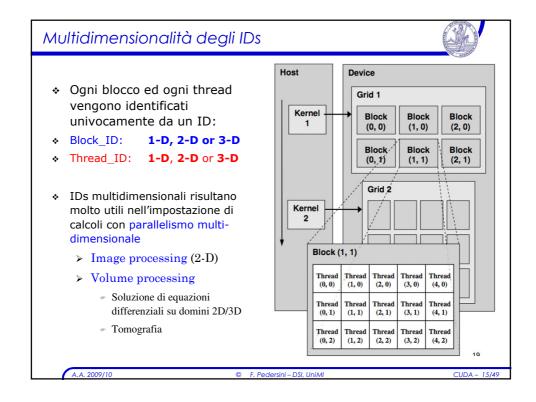

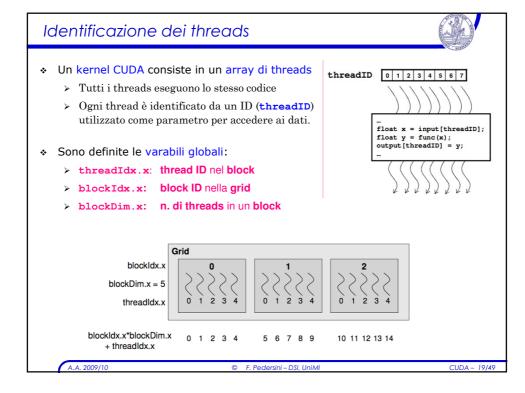

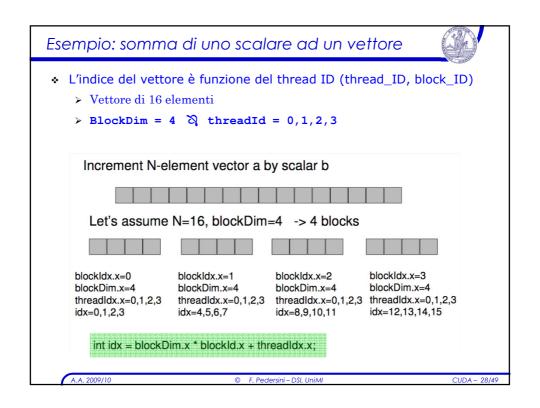

#### Terminologia CUDA

Thread: codice concorrente, eseguibile in parallelo ad altri threads su un device CUDA.

- > È l'unità fondamentale del parallelismo in CUDA

- > Rispetto ai threads CPU, nei threads CUDA i costi (tempi) di creazione e di commutazione e l'utilizzo delle risorse sono molto minori.

Warp: un gruppo di threads che possono essere eseguiti fisicamente in parallelo (SIMD – o SPMD, Single Program, Multiple Data)

> Half-warp: una delle 2 metà di un warp (spesso eseguiti sullo stesso multiprocessore)

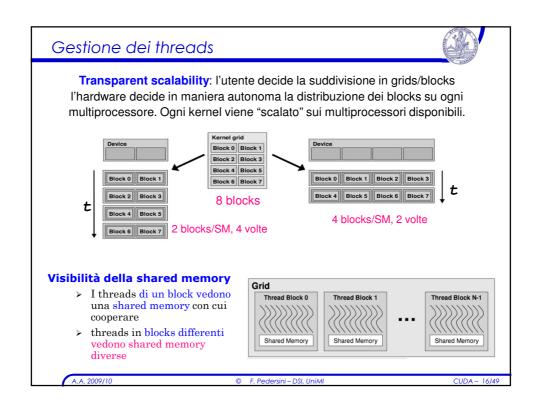

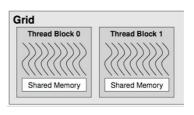

**Block**: un insieme di threads eseguiti sullo stesso Multiprocessore, e che quindi possono condividere memoria (stessa *shared memory*)

Grid: un insieme di thread blocks che eseguono un singolo kernel CUDA, in parallelismo logico, su una singola GPU

Kernel: il codice CUDA che viene lanciato (dalla CPU) su una o più GPU

A.A. 2009/1

© F. Pedersini – DSI, UniMI

CUDA - 12/49

# Considerazioni sul parallelismo in CUDA

# CUDA offre una **duplice** possibilità di **parallelismo**:

#### 1. Parallelismo funzionale

- Differenti parti di codice possono essere elaborate indipendentemente da unità funzionali separate, su differenti unità computazionali

- $\succ$  Non viene definita una associazione esplicita fra il kernel ed i multiprocessori

- > Non c'è parallelismo di kernel (viene sempre eseguito un solo kernel alla volta)

#### 2. Parallelismo sui dati

I dati vengono elaborati in parallelo mediante loro distribuzione sulle unità di elaborazione, le quali eseguono tutte pressoché la medesima funzione algoritmica (SIMT – Single Instruction, Multiple Thread).

#### Streams and kernels approach:

- > uno o più streams (flussi consistenti di dati omogenei) in ingresso possono essere elaborati da kernels e trasformati in uno o più streams in uscita

- > Il lancio del kernel funge da meccanismo di sincronizzazione

A.A. 2009/10 © F. Pedersini – DSI, UniMI CUDA – 20/49

#### Sommario

- Introduzione

- CUDA hardware

- Programmazione CUDA

- > CUDA software architecture

- > GPU memory management

- > Ottimizzazione dell'accesso ai dati

- > Sincronizzazione

- > Aspetti di calcolo

- Conclusioni

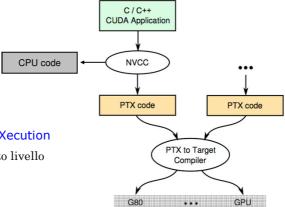

# Compilazione di codice CUDA \* CUDA API: come estensione del linguaggio C

- - > GPU Memory management

- > Comunicazione GPU-CPU

- > Programmazione e lancio di kernel

- \* Compilatore CUDA:

nvcc

\* PTX: Parallel Thread eXecution

- > GPU Assembly ad alto livello

- > Device-independent

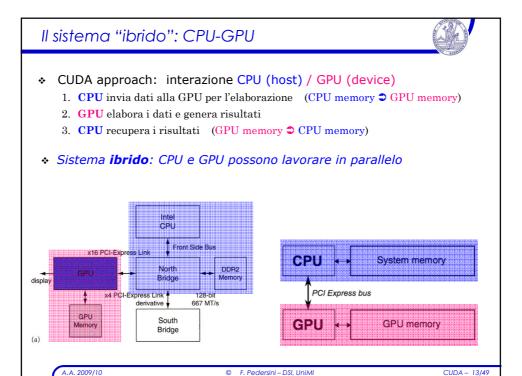

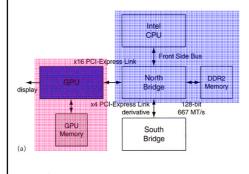

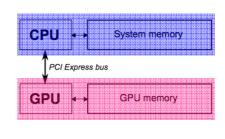

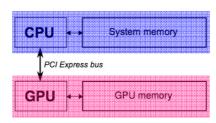

# Il sistema "ibrido": CPU-GPU

- CUDA approach: interazione CPU (host) / GPU (device)

- 1. **CPU** invia dati alla GPU per l'elaborazione (CPU memory ⊃ GPU memory)

- 2. GPU elabora i dati e genera risultati

- 3. CPU recupera i risultati (GPU memory CPU memory)

- \* Sistema ibrido: CPU e GPU possono lavorare in parallelo

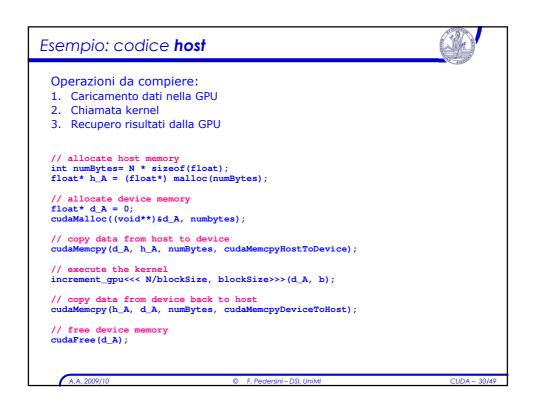

Gestione memoria della GPU

CPU e GPU dispongono di aree di memoria separate

- ❖ E' sempre l'host (CPU) a gestire la memoria del device (GPU):

- > Gestisce soltanto la **global device memory** (GPU DRAM)

- CUDA API fornisce funzioni per effettuare:

- > Allocazione dinamica: (allocate / free)

- Copia di dati tra host e device (device\_to\_host e host\_to\_device)

A.A. 2009/1

F. Pedersini – DSI, UniM

CUDA - 24/49

#### Gestione memoria della GPU

\$ GPU Memory Allocation / Release

cudaMalloc(void\*\* pointer, size\_tnbytes)

cudaMemset(void\* pointer, int value, size\_tcount)

cudaFree(void\* pointer)

int n = 1024;

int nbytes = 1024\*sizeof(int);

int \*d\_a = 0;

cudaMalloc( (void\*\*)&d\_a, nbytes);

cudaMemset( d\_a, 0, nbytes);

cudaFree(d\_a);

\* CPU-GPU Data transfer:

- > Funzione bloccante: ritorna quando la copia è completa, e non comincia la copia prima che tutte le CUDA calls precedenti siano completate.

A.A. 2009/10

F. Pedersini – DSI, UniM

CUDA - 25/4

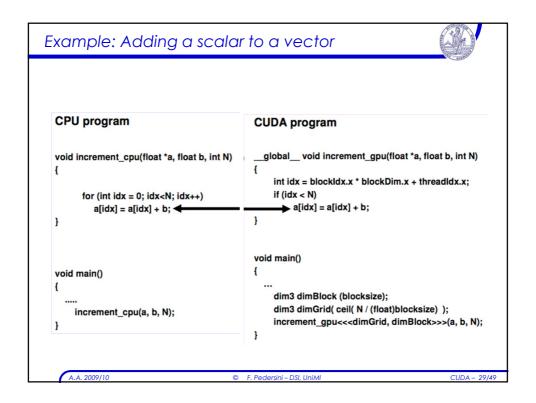

#### Primitive CUDA – definizione di funzioni

- \* Function type qualifiers: prefissi di caratterizzazione delle funzioni

- \_\_global\_\_: definisce una funzione GPU kernel. Può essere invocata solo dalla CPU (host), non dalla GPU (code must return void)

\_\_device\_\_: definisce un GPU kernel che può essere invocato solo dalla GPU stessa

- device : definisce un GPU kernel che può essere invocato solo dalla GPU stess (device), non dalla CPU (code must return void)

host : funzione eseguibile ed invocabile solo dalla CPU (host) (default)

- Lancio di un kernel:

- Call syntax:

```

kernel_func <<< dim3 grid, dim3 block >>> (...)

```

- Execution Configuration: <<< >>>:grid dimensions: x, y

- > thread-block dimensions: x, y, z

- > input arguments:

dim3 grid(16,16);

dim3 block(16,16);

kernel<<<grid, block>>>(...);

kernel<<<32, 512>>>(...);

A.A. 2009/1

F. Pedersini – DSI, UniM

CUDA - 26/49

```

Esempio: codice CUDA

Computing y = ax + y with a serial loop:

Confronto:

void saxpy_serial(int n, float alpha, float *x, float *y)

codice seriale

VS.

for(int i = 0; i < n; ++i)

y[i] = alpha*x[i] + y[i];

codice CUDA

parallelo

// Invoke serial SAXPY kernel

saxpy_serial(n, 2.0, x, y);

y[i] += a*x[i]

Computing y = ax + y in parallel using CUDA:

void saxpy_parallel(int n, float alpha, float *x, float *y)

int i = blockIdx.x*blockDim.x + threadIdx.x;

if( i<n ) y[i] = alpha*x[i] + y[i];

// Invoke parallel SAXPY kernel (256 threads per block)

int nblocks = (n + 255) / 256;

saxpy_parallel<<<nblocks, 256>>>(n, 2.0, x, y);

```

# Tipi di dato predefiniti

- In CUDA sono predefiniti alcun tipi di dato, la cui gestione ed elaborazione è ottimizzata. Possono essere usati sia in codice GPU che CPU.

- Scalar data types:

- > Standard C types: [u]char, [u]short, [u]int, [u]long, float

- > Mancava il double -> introdotto nelle ultime versioni.

- ❖ Built-in vector types

```

> [u]char[1..4],

> [u]short[1..4],

> [u]int[1..4],

> [u]long[1..4],

> float[1..4]

```

Structures accessed with x, y, z, w fields:

```

uint4 param;

int y = param.y;

```

- dim3

- Based on uint3

- > Used to specify dimensions

A.A. 2009/10

© F. Pedersini – DSI, UniMI

CUDA - 31/49

#### Variabili in CUDA

#### Variable Qualifiers (GPU code): prefissi di caratterizzazione delle variabili

- .\_\_device\_

- La variabile sarà allocata in device memory (large memory, high latency, no cache)

- > Allocazione mediante: cudaMalloc( \_\_device\_\_ qualifier ...)

- > Accessibile da tutti i threads (variabile globale)

- > Lifetime: applicazione

$\triangleright$

- - > La variabile sarà memorizzata nella shared memory (very low latency)

- > Accessibile dai threads appartenenti al medesimo block

- > Lifetime: esecuzione del kernel

- Variabili senza caratterizzazione

- > Scalari e vettori built-in: memorizzati nei registers

- > Arrays di più di 4 elementi: memorizzati in device memory

A.A. 2009/10

© F. Pedersini – DSI, UniMI

CUDA - 32/49

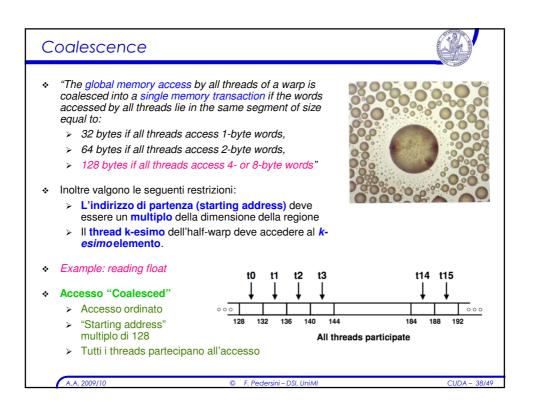

# Accesso ottimizzato alla memoria

#### Tecniche di ottimizzazione:

\* Ottimizzazione accesso alla Global memory:

Coalescence

Ottimizzazione accesso alla Shared memory:

Bank conflicts

Ottimizzazione accesso

ai dati: Texture memory

#### **Shared Memory**

- Approx. 100 volte più veloce della global memory

- > Conviene sfruttarla per ridurre l'accesso alla global memory

- \* I threads di un block possono condividere informazioni attraverso la shared memory

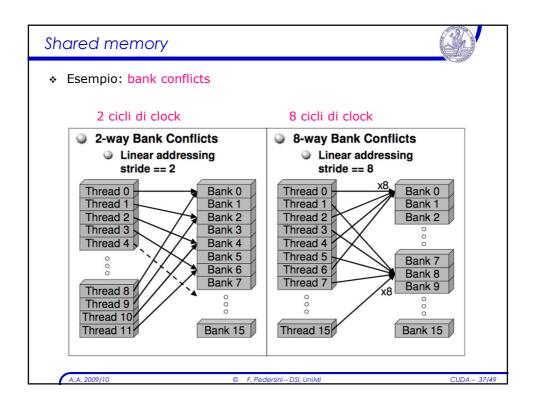

#### **Shared Memory**

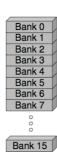

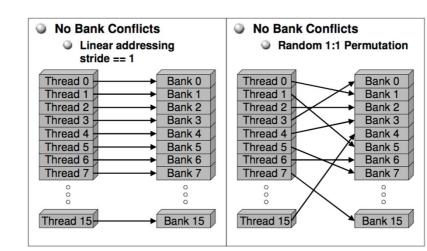

- Parallel Memory Architecture

- > di regola molti threads accedono alla shared memory simultaneamente

- ❖ La Shared memory è divisa in banchi: banks

- > Ogni banco può "servire" un thread per ciclo di clock

- > La shared memory può "servire" simultaneamente tanti threads quanti sono i banchi (GeForce 8x: 16 threads per SM 3 16 banks)

- \* Accesso simultaneo...

- ... a banchi differenti avviene in parallelo (1 ciclo di clock)

- ... allo stesso banco causano un bank conflict

- > l'accesso avviene quindi in modo serializzato

- La Shared memory è veloce come i registri, se non ci sono conflitti!

A.A. 2009/10

E Pedersini – DSI UniM

CUDA - 35/49

# Shared memory

Esempio: nessun conflitto

A.A. 2009/

F. Pedersini – DSI, UniMI

CUDA - 36/49

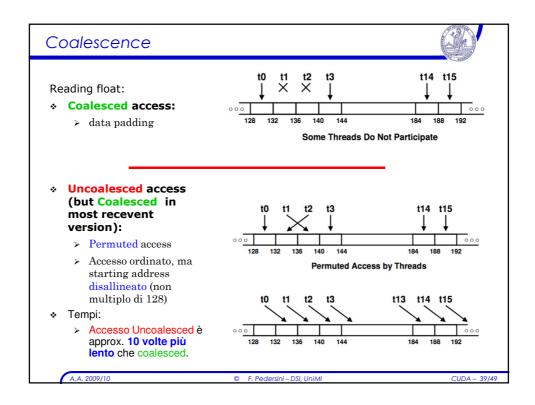

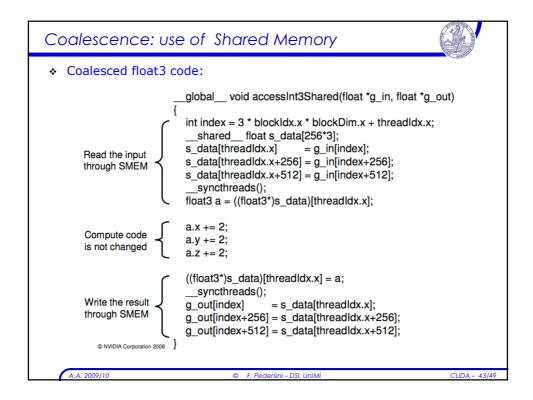

#### Coalescence

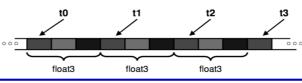

\* Example: uncoalesced float3 code

```

__global__ void accessFloat3(float3 *d_in, float3 d_out)

{

int index = blockIdx.x * blockDim.x + threadIdx.x;

float3 a = d_in[index];

a.x += 2;

a.y += 2;

a.z += 2;

d_out[index] = a;

}

```

- float3 is 12 bytes, ≠ 4, 8, or 16

- > Each thread ends up executing 3 reads

- > Half-warp reads three (16\*4=64 Byte)-wide non-contiguous regions

.A. 2009/10 © F. Pedersini – DSI, UniMI CUDA

#### Coalescence: SoA vs. AoS

Strategie per evitare l'accesso uncoalesced:

- Uso di Structure of Arrays (SoA) al posto di Array of Structures (AoS)

- \* Se SoA non è utilizzabile:

- > Forzo l'allineamento: \_\_align (X), X = 4, 8, or 16

- > Uso Shared Memory

float3: X Y Z

AoS: X Y Z X Y Z X Y Z X Y Z

#### Coalescence: use of Shared Memory

- Use shared memory to allow coalescing

- Need sizeof (float3) \* (threads/block) bytes of SMEM

- > Each thread reads 3 scalar floats:

- > Offsets: 0, (threads/block), 2\*(threads/block)

- ➤ These will likely be processed by other threads ≥ coalescence!

- Processing

- > Each thread retrieves its float3 from SMEM array

- > Use thread ID as index

- $\succ$  Rest of the code does not change!

A.A. 2009/1

F. Pedersini – DSI, UniM

CUDA - 42/49

# **Textures** \* Texture è un oggetto per lettura dati, che presenta diversi vantaggi rispetto alla Constant Memory: Presenza di cache (ottimizzata per località Device > Interpolazione hardware (linear, bi-, tri-Multiprocessor 2 > Wrap modes (per indirizzi "out-of-bounds") Indirizzabile in 1D, 2D, or 3D Possibilità di accesso con coordinate integer o normalized coordinates Uso: > CPU code: data binding a texture object > Kernel accede alla texture chiamando una fetch function: tex1D(),tex2D(),tex3D()

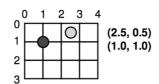

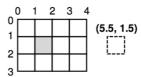

# Texture Addressing

#### **Interpolazione:**

> Es: interpolazione bilineare:

$$V(2.5,0.5) = \frac{1}{4} (V(2,0) + V(3,0) + V(2,1) + V(3,1))$$

# Wrap modes:

- Wrap

- Coordinate Out-of-bounds coordinate vengono "arrotolate" (modulo DIM)

- Clamp

- > Coordinate Out-of-bounds sono sostituite dal bordo più vicino

A.A. 2009/1

F. Pedersini – DSI, UniM

CUDA - 45/49

### Sincronizzazione tra threads

#### void \_\_syncthreads();

- > Sincronizza tutti i threads di un block

- > Genera una barriera di sincronizzazione: nessun thread può superare la barriera finché non l'hanno raggiunta tutti.

- > Usato per evitare gli RAW / WAR / WAW hazards nell'accesso alla shared memory

- È permesso in codice condizionale (presenza di branch) solo se la condizione è uniforme su tutti i threads del blocco.

#### Atomic operations su interi memorizzati nella global (device) memory:

- > Operazioni associative su interi signed/unsigned: add, sub, min, max, and, or, xor, increment, decrement, compare, swap, ...

- > atomic\_add(), atomic\_sub(), ...

A.A. 2009/1

© F. Pedersini – DSI, UniMI

CUDA - 46/49

#### Math issues

- ❖ Double precision -> Introdotta con l'ultima generazione di schede.

- ❖ Deviazioni dallo standard IEEE-754

- > Divisione non-compliant

- Non tutti i rounding modes sono supportati

- > Numeri denormalizzati non supportati Alcune eccezioni FPU non segnalate

|                                       | G8x                                | SSE                                              | IBM Altivec                    | Cell SPE                    |

|---------------------------------------|------------------------------------|--------------------------------------------------|--------------------------------|-----------------------------|

| Format                                | IEEE 754                           | IEEE 754                                         | IEEE 754                       | IEEE 754                    |

| Rounding modes for<br>FADD and FMUL   | Round to nearest and round to zero | All 4 IEEE, round to<br>nearest, zero, inf, -inf | Round to nearest only          | Round to zero/truncate only |

| Denormal handling                     | Flush to zero                      | Supported,<br>1000's of cycles                   | Supported,<br>1000's of cycles | Flush to zero               |

| NaN support                           | Yes                                | Yes                                              | Yes                            | No                          |

| Overflow and Infinity support         | Yes, only clamps to max norm       | Yes                                              | Yes                            | No, infinity                |

| Flags                                 | No                                 | Yes                                              | Yes                            | Some                        |

| Square root                           | Software only                      | Hardware                                         | Software only                  | Software only               |

| Division                              | Software only                      | Hardware                                         | Software only                  | Software only               |

| Reciprocal estimate accuracy          | 24 bit                             | 12 bit                                           | 12 bit                         | 12 bit                      |

| Reciprocal sqrt estimate accuracy     | 23 bit                             | 12 bit                                           | 12 bit                         | 12 bit                      |

| log2(x) and 2^x<br>estimates accuracy | 23 bit                             | No                                               | 12 bit                         | No                          |

#### Conclusioni

- Caratteristiche principali di CUDA ("Design Goals"):

- Hardware:

- > Scalabilità verso centinaia di cores / migliaia di threads paralleli

- > Gerarchia di memoria semplice e potente

#### Software:

- > Estensione minimale al linguaggio C

- Veloce curva di apprendimento: permette ai programmatori di concentrarsi sugli algoritmi, anziché sulle regole di programmazione parallela

- CUDA programming "golden rules":

- > Use parallelism efficiently

- > Coalesce memory accesses if possible

- > Take advantage of shared memory

- > Explore other memory spaces: Texture, Constant

- > Reduce bank conflicts

A.A. 2009/10 © F. Pedersini – DSI, UniMI CUDA – 48/49

#### Conclusioni

- \* È CUDA il futuro del calcolo ad alte prestazioni?

- Multicore vs. DSP:

- \* NVIDIA G8x:

- > 200 € / 16 Multiprocessors

- $\succ$  complete system < 1,000 €

- $\succ$  Software development tools: 0 €

- DSP (TI):

- 10 € / processor

- complete system (hi-perf) > 10,000 €

- Software development tools: ~ 5000 €

- \* Altre soluzioni multicore: IBM/Toshiba CELL Processor (PS3)

- \* Riferimenti:

#### www.nvidia.com/cuda

- > Documentazione: CUDA Programming Guide, CUDA Reference Manual

- > Software (free): CUDA SDK (Windows, Linux, Mac OS/X), CUDA drivers, ...

- > CUDA forum

A.A. 2009/10

© F. Pedersini – DSI, UniMI

CUDA - 49/49